## CS344 – Lecture 3 DEVELOPMENT TOOLS

# P4.org BMu2

CS344, Stanford University

- Office Hours:

- Tuesdays & Thursdays: 3 5pm, Gates 315

- Lab Access

- Tutorial Exercises (Due Thursday 4/11 11:59pm)

- No Lecture on Wednesday

- Tutorial exercises

- Interoperability planning

- Router project

- Guest Lecture on Monday

#### **Development Tools**

#### SimpleSumeSwitch

### $P_4 \rightarrow NetFPGA P4.org BMv2$

**NetFPGA SUME**

CS344, Stanford University

Mininet

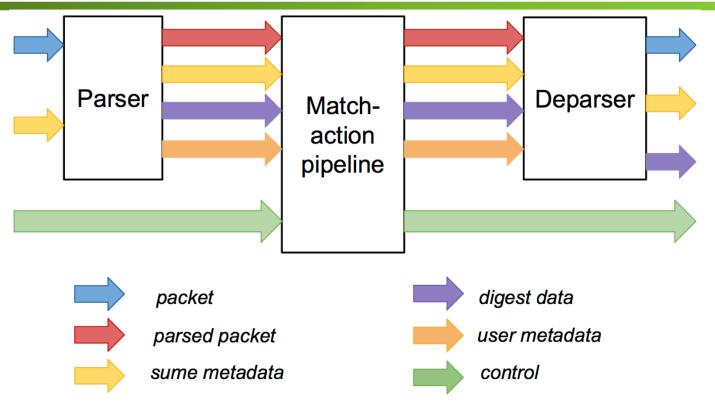

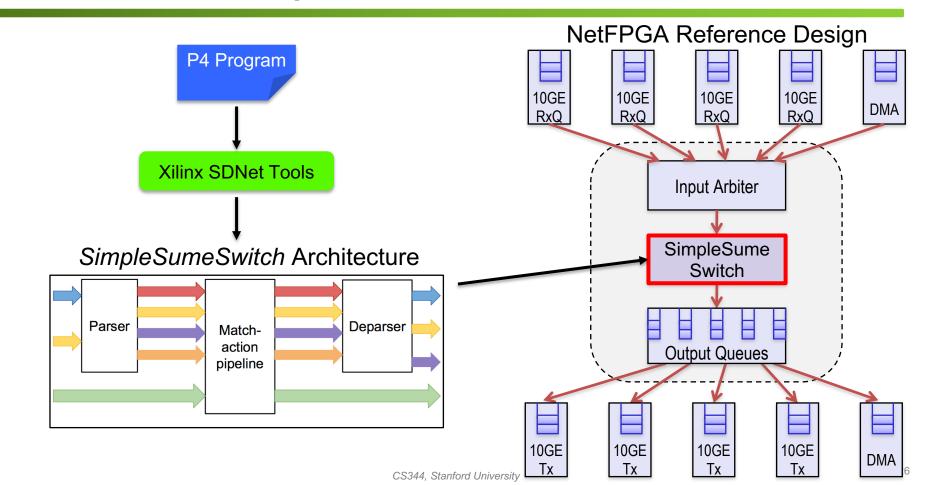

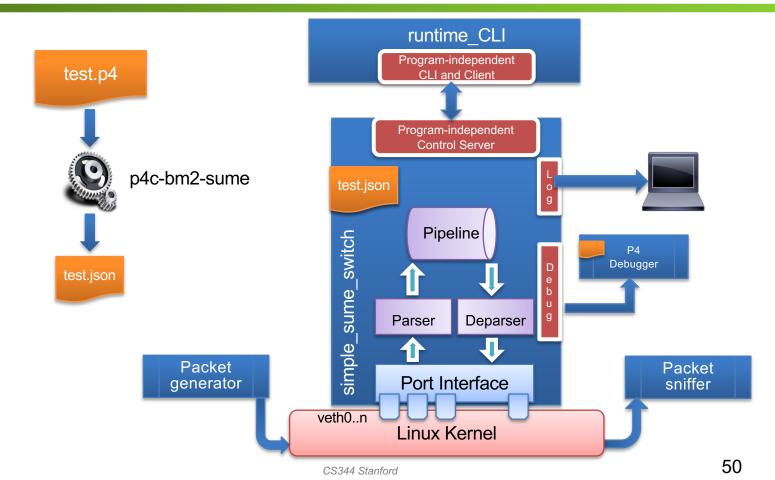

#### SimpleSumeSwitch Architecture Model for SUME Target

• P4 used to describe parser, match-action pipeline, and deparser

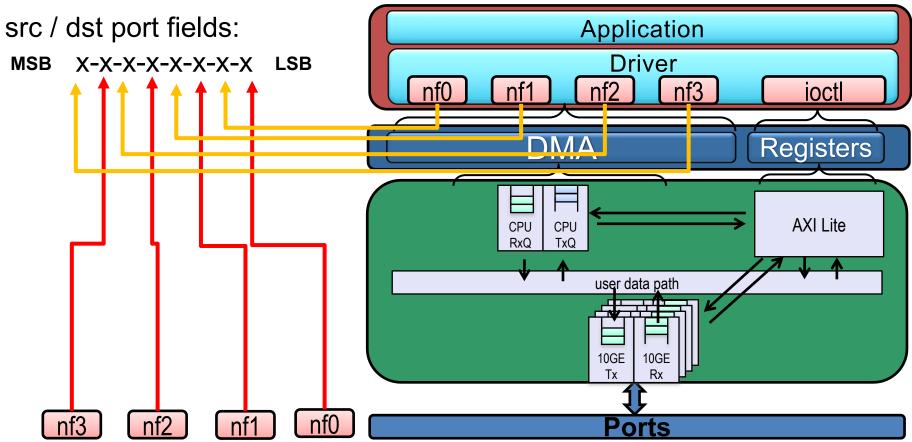

#### Standard Metadata in SimpleSumeSwitch Architecture

```

/* standard sume switch metadata */

struct sume metadata t {

bit<16> dma q size;

bit<16> nf3 q size;

bit<16> nf2 q size;

bit<16> nf1 q size;

bit<16> nf0 q size;

// send digest data to CPU

bit<8> send dig to cpu;

// ports are one-hot encoded

bit<8> dst port;

bit<8> src port;

// pkt len is measured in bytes

bit<16> pkt len;

```

- src\_port/dst\_port one-hot encoded, easy to do multicast

- \*\_q\_size size of each output queue, measured in terms of 32byte words, when packet starts being processed by the P4 program

#### **P4** Parsing

```

parser MyParser(packet in packet,

out headers hdr,

out user_data_t user,

out digest data t digest,

inout sume metadata_t smeta)

state start {

packet.extract(hdr.ethernet);

transition select(hdr.ethernet.type) {

0x800

: parse ipv4;

default : accept;

state parse ipv4 {

packet.extract(hdr.ipv4);

transition accept;

```

- Map packets into headers and metadata

- State machine

- Three predefined states:

- start

- accept

- reject

- User defined states

- Loops are OK

#### **P4 Match-Action Processing**

```

control MyIngress(inout headers hdr,

inout user data t user,

inout digest data t digest,

inout sume metadata t smeta) {

action set dst port(bit<8> port) {

smeta.dst port = port;

}

table forward {

key = { smeta.src_port : exact; }

actions = { set dst port; }

size = 1024;

default action = set dst port(0);

apply {

if (hdr.ipv4.isValid()) {

forward.apply();

else {

smeta.dst port = 0;

```

- Declare tables and actions

- Similar to C functions

- No loops

- Functionality specified by code in apply statement

- Table entries populated by control-plane

#### forward table entries:

| Key | Action Name  | Action Data |

|-----|--------------|-------------|

| 1   | set_dst_port | 2           |

| 2   | set_dst_port | 1           |

#### **P4 Deparsing**

inout digest\_data\_t digest, inout sume\_metadata\_t smeta) {

apply {

```

// insert valid headers into packet

packet.emit(hdr.ethernet);

packet.emit(hdr.ipv4);

```

Assembles the headers back

into a well-formed packet

Header is only emitted if it valid

#### **P4 Externs**

. . .

// special SUME hash function

extern void sume\_hash(in bit<64> data, out bit<8> result);

```

apply {

bit<8> flowID;

sume_hash(hdr.ip.src++hdr.ip.dst, flowID);

```

- Black boxes for P4 programs

- Functionality is not described in P4

- Used to perform device/vendor specific functionality

- Can be stateless of stateful

- Can be accessed by the controlplane

- Set of supported externs is

defined by architecture

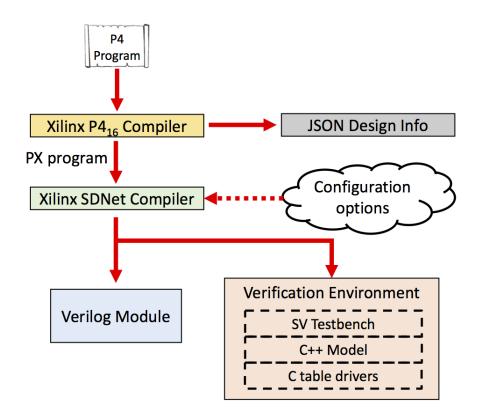

#### **Xilinx SDNet Compiler**

- P4 to PX frontend

- Produces:

- $\circ$  JSON design info

- $\circ$  HDL module

- Verification environment

- Configuration:

- Throughput (1 400 Gbps)

- Latency

- $\circ$  Resources

CS344, Stanford University

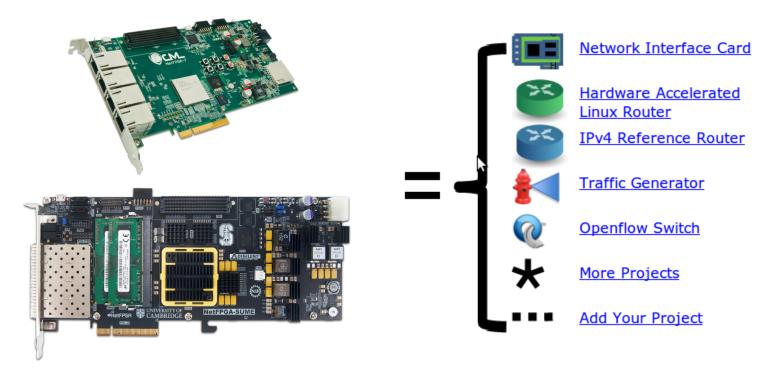

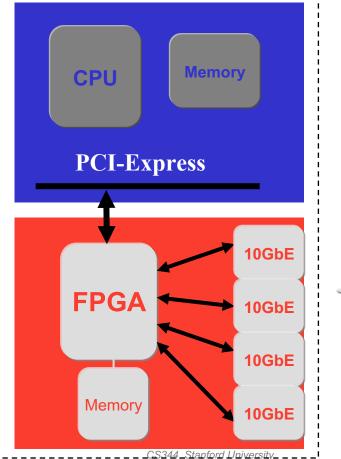

#### **NetFPGA = Networked FPGA**

• A line-rate, flexible, <u>open networking platform</u> for teaching and research

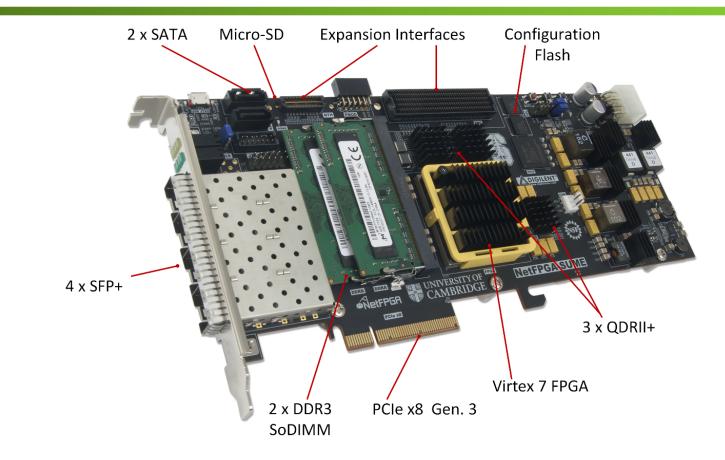

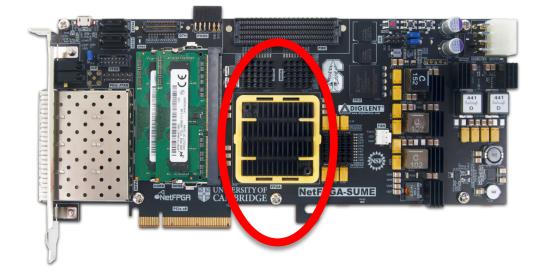

#### **NetFPGA-SUME**

#### Xilinx Virtex 7 690T

- Optimized for highperformance applications

- 690K Logic Cells

- 52Mb RAM

- 3 PCIe Gen. 3 Hard cores

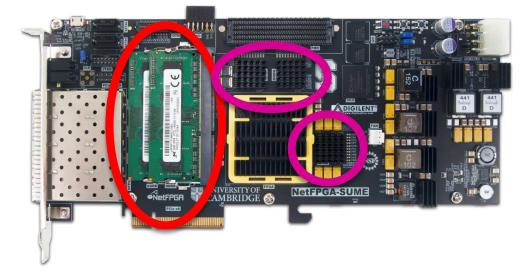

#### **Memory Interfaces**

- DRAM:

2 x DDR3 SoDIMM

1866MT/s, 4GB

- SRAM: 3 x 9MB QDRII+, 500MHz

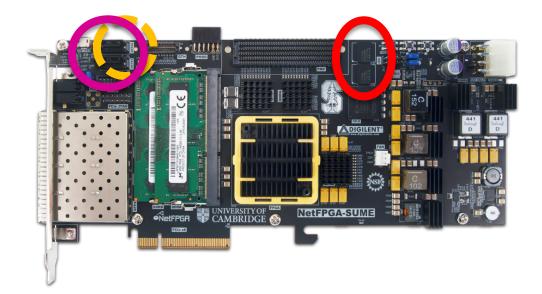

#### **Host Interface**

- PCle Gen. 3

- x8 (only)

- Hardcore IP

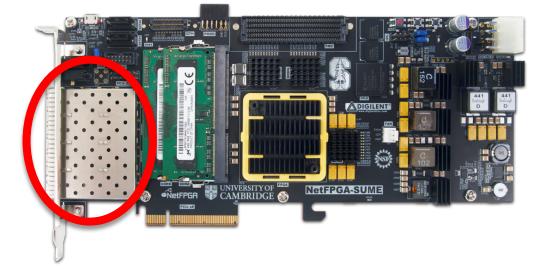

#### **Front Panel Ports**

- 4 SFP+ Cages

- Directly connected to the FPGA

- Supports 10GBase-R transceivers (default)

- Also Supports 1000Base-X transceivers and direct attach cables

#### Storage

- 128MB FLASH

- 2 x SATA connectors

- Micro-SD slot

- Enable standalone operation

#### **NetFPGA** board

Networking Software running on a standard PC

A hardware accelerator built with FPGA driving 1/10/ 100Gb/s network links

PC with NetFPGA

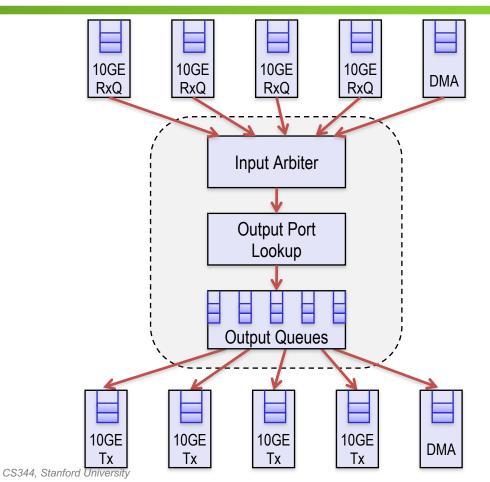

#### **NetFPGA Reference Design**

- Five stages

- $\circ$  Input port

- $\circ$  Input arbitration

- Forwarding decision and packet modification

- $\circ$  Output queuing

- $\circ$  Output port

- 256-bit data bus

- 200 MHz

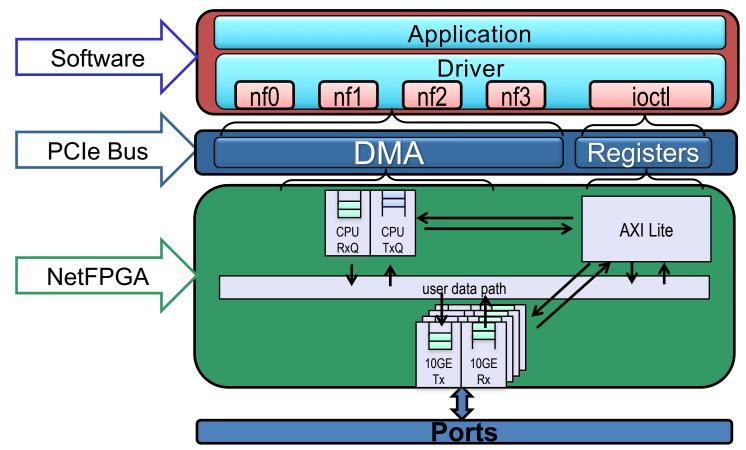

#### **Full System Components**

CS344, Stanford University

#### **Interface Naming Conventions**

24

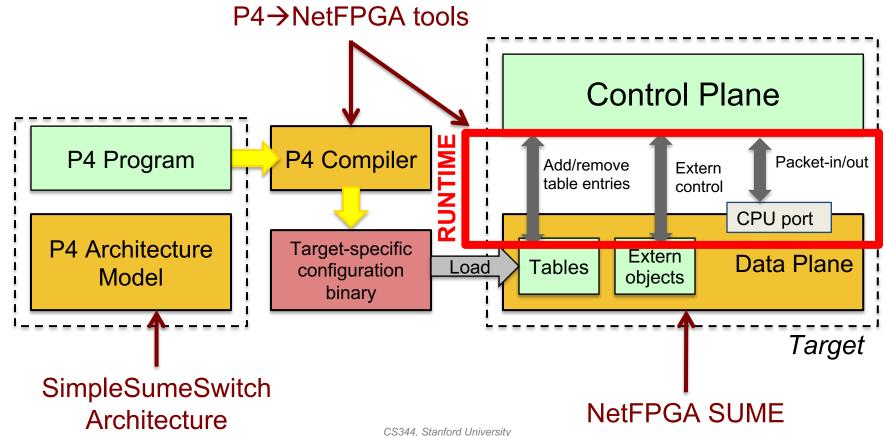

# P→ NetFPGA Overview

CS344, Stanford University

#### **General Process for Programming a P4 Target**

#### P4→NetFPGA Compilation Overview

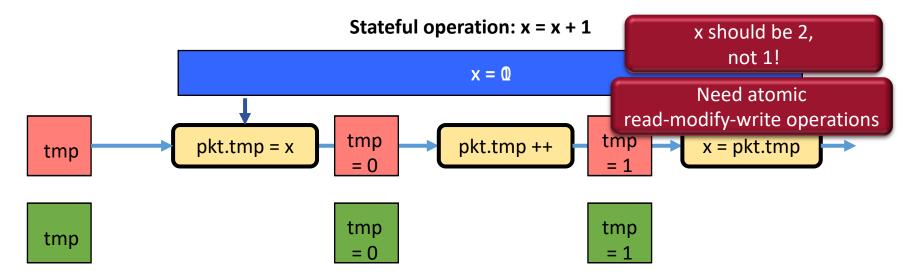

#### P4→NetFPGA Extern Function library

- HDL modules invoked within P4 programs

- Stateless reinitialized for each packet

- Stateful keep state between packets

- · Cannot pipeline stateful operations

#### P4→NetFPGA Extern Function library

#### •Stateful Atoms[1]

| Atom      | Description                                            |

|-----------|--------------------------------------------------------|

| R/W       | Read or write state                                    |

| RAW       | Read, add to, or overwrite state                       |

| PRAW      | Predicated version of RAW                              |

| ifElseRAW | Two RAWs, one each for when predicate is true or false |

| Sub       | IfElseRAW with stateful subtraction capability         |

| <ul> <li>Stateless Externs</li> </ul> | Atom        | Description                                         |

|---------------------------------------|-------------|-----------------------------------------------------|

|                                       | IP Checksum | Given an IP header, compute IP checksum             |

|                                       | LRC         | Longitudinal redundancy check, simple hash function |

| <ul><li>Add your own!</li></ul>       | timestamp   | Generate timestamp (granularity of 5 ns)            |

[1] Sivaraman, et al. "Packet transactions" ACM SIGCOMM Conference, 2016.

CS344, Stanford University

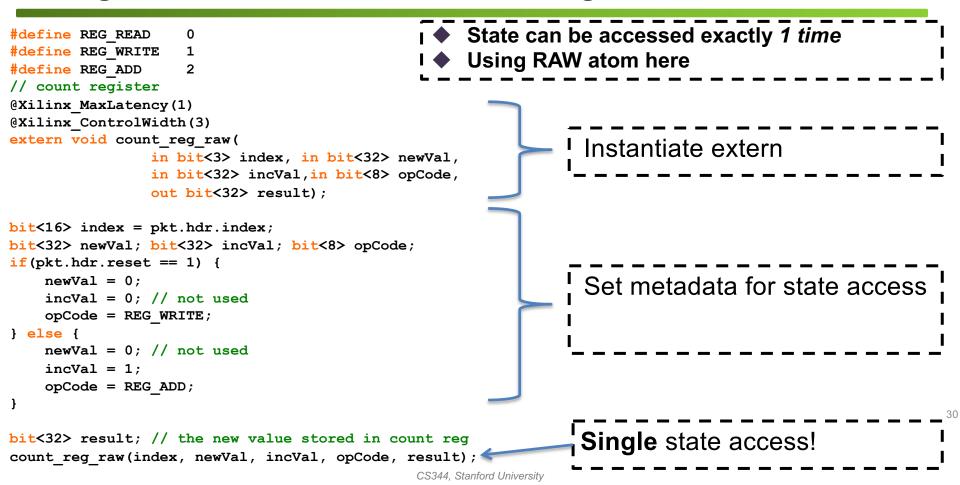

#### **Using Atom Externs in P4 – Resetting Counter**

Packet processing pseudo code:

```

count[NUM_ENTRIES];

```

```

if (pkt.hdr.reset == 1):

count[pkt.hdr.index] = 0

else:

```

count[pkt.hdr.index]++

#### **Using Atom Externs in P4 – Resetting Counter**

#### **Adding Custom Extern Functions**

1. Implement Verilog extern module in

\$SUME\_SDNET/templates/externs/

2. Add entry to \$SUME\_SDNET/bin/extern\_data.py

- No need to modify any existing code

- AXI Lite control interface

#### P4→NetFPGA Simulations

- Python Scapy based script to generate test packets and metadata

- Two stages of simulations:

- Testbench produced by SDNet compiler

- Full NetFPGA pipeline simulation

#### **API & Interactive CLI Tool Generation**

- Both Python API and C API

- Manipulate tables and externs in P4 pipeline

- Used to implement control-plane

- CLI tool

- Useful debugging feature

- Query various compile-time information

- Interact directly with tables and externs at run time

#### P4→NetFPGA Workflow

- 1.Write P4 program

- 2.Write externs

fail

pass

3.Write python gen\_testdata.py script

All of your effort will go here

- 4.Compile to Verilog / generate API & CLI tools

- 5.Run simulations

- ▲ 6.Build bitstream

- 7.Check implementation results

- 8.Test the hardware

#### P4→NetFPGA Online Tutorials[1]

- Step-by-step guide

- Solutions available

- Three assignments:

- Switch as calculator

- $\circ$  TCP flow monitor

- In-band Network Telemetry (INT)

[1] <u>https://github.com/NetFPGA/P4-NetFPGA-public/wiki/Tutorial-Assignments</u>

#### P4→NetFPGA Community

- 150 different institutions

- Mailing list: <u>cl-netfpga-sume-beta@lists.cam.ac.uk</u>

#### **Debugging P4 Programs**

- SDNet HDL simulation

- SDNet C++ simulation

- Verbose packet processing info

- Output PCAP file

- Full SUME HDL simulation

## **Directory Structure of \$SUME\_FOLDER**

```

P4-NetFPGA-live/

```

```

- contrib-projects/

```

|- sume-sdnet-switch/  $\rightarrow$  the main directory for P4 dev

|- lib/  $\rightarrow$  contains all of the SUME IP cores

- tools/  $\rightarrow$  various NetFPGA scripts for test infra.

- Makefile  $\rightarrow$  builds all of the SUME IP cores

## **Directory Structure of \$SUME\_SDNET**

```

sume-sdnet-switch/

```

```

|- bin/ \rightarrow scripts used to automate workflow

```

|- projects/  $\rightarrow$  all of the P4 project directories

```

- switch_calc/

```

### **Directory Structure of \$P4\_PROJECT\_DIR**

```

$P4_PROJECT_DIR/

```

- src/  $\rightarrow$  P4 source files and commands.txt

- testdata/ → scripts to generate testdata used for verifying functionality of P4 program

- simple\_sume\_switch/ → main SUME project directory, top level HDL files and SUME sim scripts

- sw/ → populated with API files and CLI tools and any user software for the project

- nf\_sume\_sdnet\_ip/  $\rightarrow$  SDNet output directory

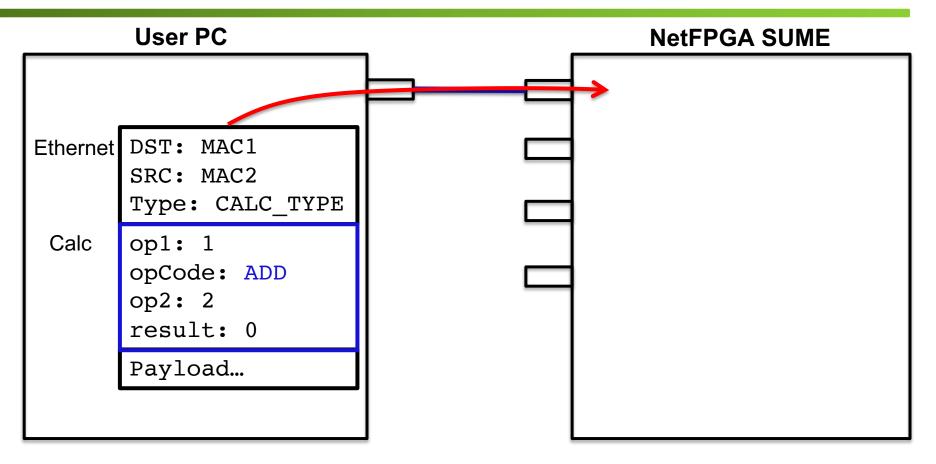

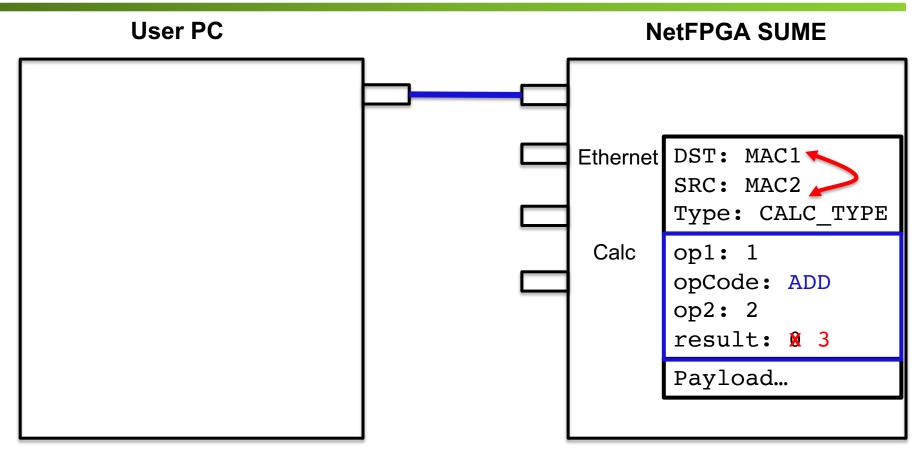

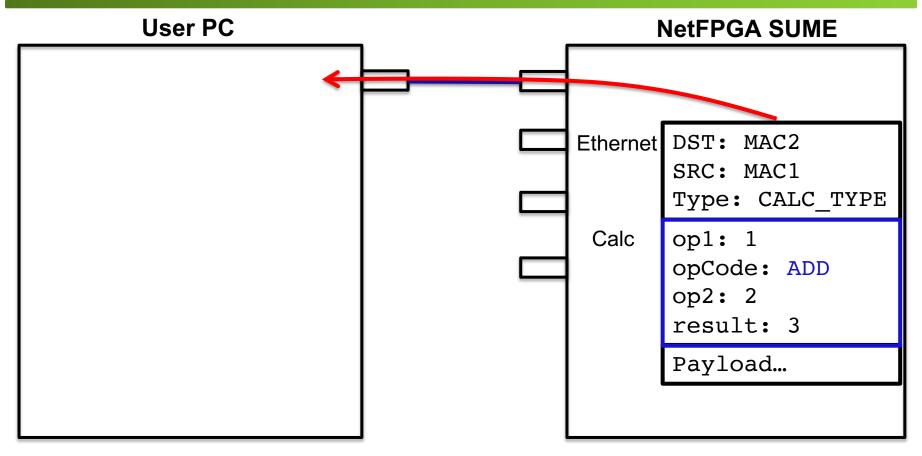

## **Assignment 1: Switch as a Calculator**

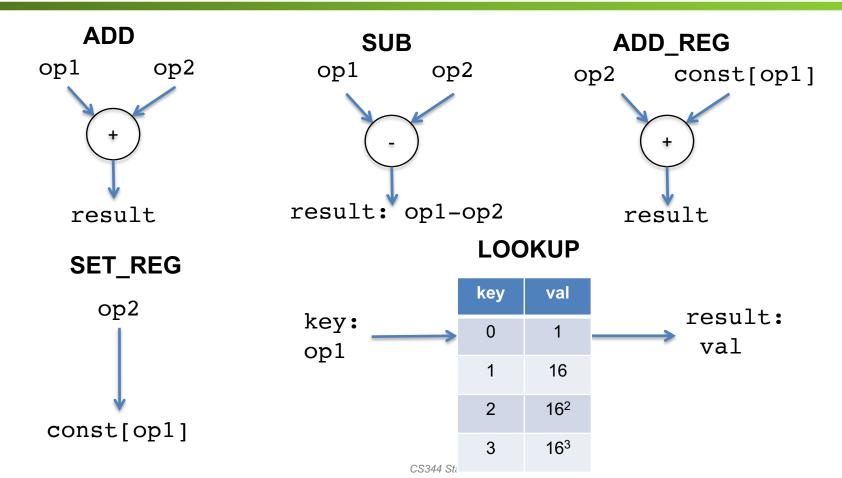

#### Supported Operations

- ADD add two operands

- SUBTRACT subtract two operands

- ADD\_REG add operand to current value in the register

- SET\_REG overwrite the current value in the register

- LOOKUP Lookup the given key in the table

```

header Calc_h {

bit<32> op1;

bit<8> opCode;

bit<32> op2;

bit<32> result;

```

### **Switch Calc Operations**

## P4.org BMv2 Mininet Emulation

# **Virtual Machine**

#### • Dependencies:

- Bmv2

- p4c

- Mininet

### • Getting Set Up:

- Install Vagrant and VirtualBox

- \$ git clone -b si/skt/SimpleSumeSwitch https://github.com/CS344-Stanford/tutorials.git

- \$ cd tutorials/vm

- \$ vagrant up

• C++ packet processing library for P4 programs

|                            | Mininet<br>(Network Emulator)                      | NS3<br>(Network Simulator) |

|----------------------------|----------------------------------------------------|----------------------------|

| Supported<br>Architectures | <ul><li>V1Model</li><li>SimpleSumeSwitch</li></ul> | P4QueueDisc                |

## **Behavioral Model v2**

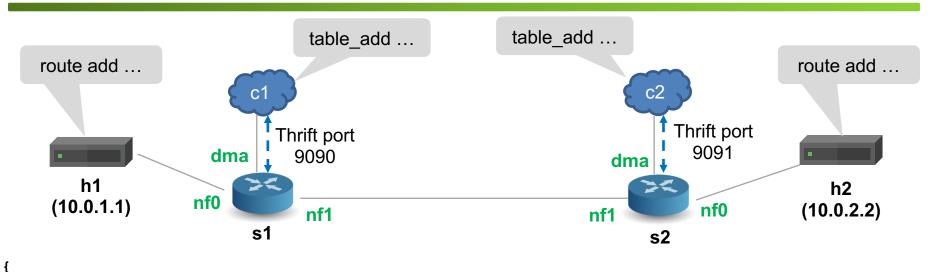

## **Mininet Topology**

}

```

"hosts": {

"h1": {"ip": "10.0.1.1/24", "mac": "08:00:00:00:01:01",

"commands":["route add default gw 10.0.1.10 dev eth0"]},

"h2": {"ip": "10.0.2.2/24", "mac": "08:00:00:00:02:02",

"commands":["route add default gw 10.0.2.20 dev eth0"]}

},

"switches": { "s1": {"cli_input": "s1-commands.txt"},

"s2": {"cli_input": "s2-commands.txt"} },

"links": [ ["h1", "s1-nf0"], ["s1-nf1", "s2-nf1"], ["h2", "s2-nf0"] ]

```

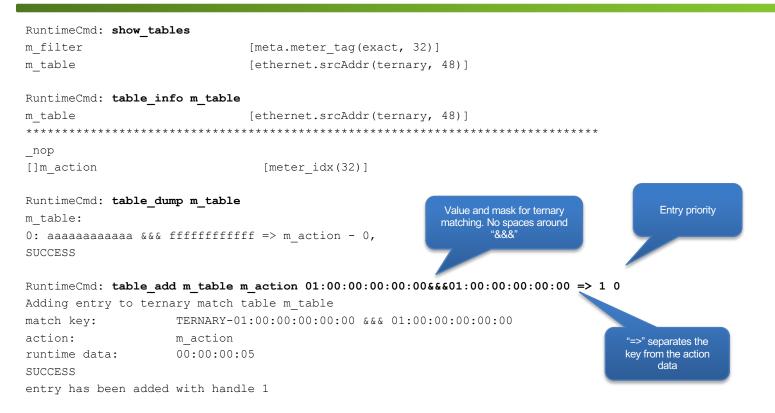

## Working with Tables in runtime\_CLI

# SimpleSumeSwitch Support in bmv2

- No extern support

- No data-plane broadcasting

- No digest\_data support

- Different CLI commands from P4→NetFPGA

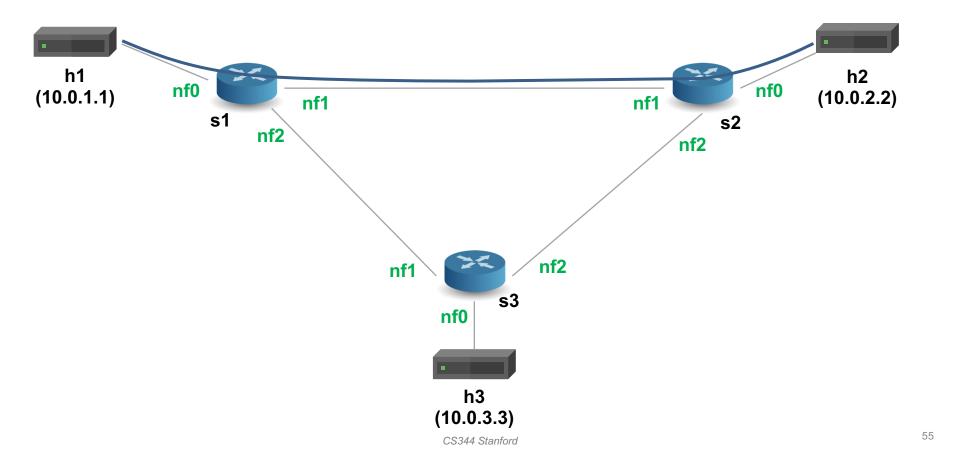

# **Basic Exercise**

#### • Basic Router Functionality:

- Parse Ethernet and IPv4 headers

- Find destination in IPv4 routing table

- Update source / destination MAC addresses

- Decrement time-to-live (TTL) field

- Update IPv4 checksum

- Set egress port

- Deparse header back into packet

- Starter code in basic.p4

- Static control-plane

## **Basic Exercise**

## FIN